Tartalom

Rendszerszintű szintézis

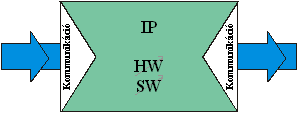

A mikroelektronikai ipar állandó gyors fejlődése egyre bonyolultabb, „intelligens”, (Intellectual Property, IP) készen kapható funkcionális egységeket kínál építőelemekként a tervezőknek. Az ilyen komponensek (IP-k) adaptálhatósága, programozhatósága és rekonfigurálhatósága kedvező lehetőséget nyújt azonos típusok ismételt felhasználására (reusing). Ezáltal a piacra kerülés ideje jelentősen csökkenhet, mert a tesztelés és a gyors prototipus-készítés kisebb ráfordítást igényel.

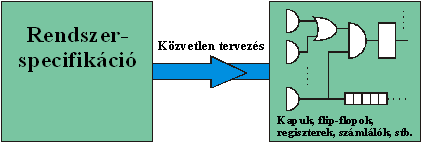

Ezzel szemben a többé-kevésbé egzakt logikai szintézis módszertana, amely viszonylag egyszerű építőelemek (kapuk, flip-flopok, regiszterek, számlálók, stb.) alkalmazásán alapul, gyökeres kiegészítésre szorul.

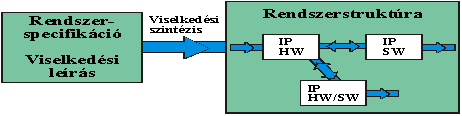

A megoldandó feladatból kiinduló rendszerspecifikáció ugyanis már elképzelhetetlen a komplex építőelemeknek (IP-knek), konkrét fizikai erőforrásokként való kezelésével. Jóval magasabb absztrakciós szintről kell indítani a tervezési folyamatot, amelyet emiatt rendszerszintű szintézisnek (system-level synthesis, SLS) neveznek. A kiindulási magas absztrakciós szinten az ú.n. viselkedési specifikációból (behavioral specification) kell kiindulni, amely fiktív viselkedési összetevők együttműködésének leírása.

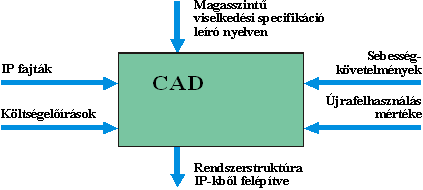

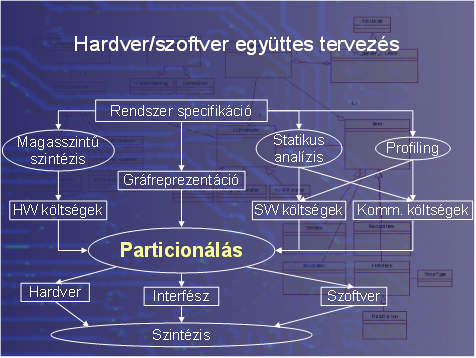

A rendszerszintű szintézis további lépéseiben olyan dekompozíciós algoritmusra van szükség, amely a teljes rendszert felbontja előre definiált IP-kre. Ennek során sokszor egymásnak ellentmondó peremfeltételek mellett (az IP-k közötti kommunikáció sebessége, a vezérlési struktúra egyszerűsége, az ismételt felhasználás mértéke, a különböző költségtényezők egymáshoz képesti aránya, pipe-line működés biztosítása, stb.) kell a lehető legkedvezőbb megoldásokat megtalálni, lehetőleg szisztematikus lépésekben.. A gyártók egyre növekvő választékát kínálják az IP-knek, katalógusaikban többnyire viselkedési szintű specifikációval. Az IP-k között teljesen programozható cél- és általános processzorok is megjelennek (pl. DSP). Ezáltal a rendszerszintű szintézis egyre inkább olyan felépítést eredményez, amely hardware és software összetevőket egyaránt tartalmaz. Így az ún. hardware-software együttes tervezés (hardware-software codesign) része a rendszerszintű szintézisnek.

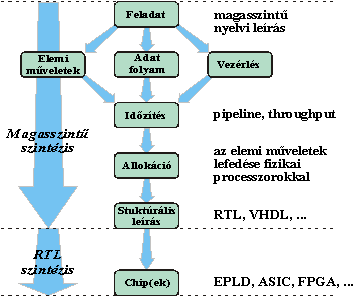

A tervezés automatizálása (design automation) döntő jelentőségű a rendszerszintű szintézisben, mert a legtöbb lépés NP-teljes jellegű, így a nem mindig kerülhetők el a közelítő optimumkereső eljárások. A technológiai fejlődés következtében egyre komplexebb rendszerek hozhatók létre egyetlen integrált áramköri tokban (System on Chip, SoC) a fentiekben vázolt felülről lefelé haladó (top-down) metodika szerint a magas absztrakciós szintű viselkedési specifikációból kiindulva. A magas szintű specifikáció általában valamilyen magas szintű programnyelven történik, miáltal a számítógéppel segített automatikus tervező eljárások (CAD tools) bemeneti adatai közvetlenül képezhetők. A viselkedési szintről kiinduló szisztematikus tervezési lépéseket elsőként az ún. magasszintű szintézishez (high-level synthesis, HLS) kezdték alkalmazni a 80-as évek közepétől. A HLS algoritmusok főként a nagysebességű célhardware-ként megvalósított jelfeldolgozó eszközök struktúrájának optimalizálását támogatták. A valóságos hardware erőforrások, mint összetevők ekkor már elég komplexek voltak ahhoz (de korántsem annyira komplexek, mint az IP-k ma és a jövőben), hogy leírásukat már viselkedési szinten legyen célszerű kezelni fiktív elemi műveletekből összeállítva. A HLS algoritmusok többsége kiterjeszthető és alkalmazható a rendszerszintű szintézis céljaira. Ezen belül a HLS algoritmusok előnyösen alkalmazhatók pl. az IP-k tervezéséhez. A legtöbb alkalmazási területen a sebességi követelmények igénylik az ún. pipeline feldolgozás megvalósítását. Ezért a HLS algoritmusoknak támogatniuk kell a pipeline üzemmódban is működtethető struktúrák optimalizálását.

Számos nem műszaki területeken is hasznos a rendszerszintű tervezés és optimalizálás, különös tekintettel a pipeline működési mód megvalósítására. Példaként említhetők erre azok a folyamatok, amelyeket különböző üzleti területeken alkalmaznak, pl. az emberi erőforrás gazdálkodás, a logisztika vagy a pénzügyi algoritmusok. Ezek a tevékenységek is felbonthatók további részfolyamatokra és elemi lépésekre. A logisztikai területeken, például a vevői rendelések kezelése során a számlázást és kifizetést megelőzik az árajánlatkérés, ajánlat, megrendelés, szállítás, számlaellenőrzés részfolyamatok. Hasonló példák sorolhatók még pl. az anyaggazdálkodás, a termelés, gyártás, pénzügy, kontrolling folyamataiban. A cégek széleskörűen alkalmazzák a „legjobb gyakorlat (best practices)” üzleti megoldásokat, amelyeket az ú.n. ERP rendszerek több évtizedes használata, tapasztalata munkált ki. A hatékonyság érdekében mégis érdemes ezeket a megoldásokat megvizsgálni a rendszerszintű tervezés elveinek alkalmazhatósága szempontjából a pipeline üzemmódra való optimalizált tervezés céljából. Számos olyan eset fordulhat elő ugyanis, amikor a megszokott üzleti gyakorlatot, szokást érdemes megváltoztatni ennek érdekében.